## 應用電子學 複習 第七章

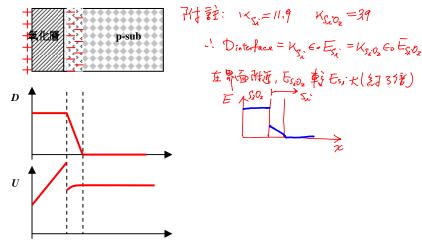

1. 一個 n-MOSFET 閘極剛加少量正電偏壓時,通道會形成空乏區,請畫出由氧化層到空乏區及半導體基板的電位移(或電力線密度)及電子電位能的分布圖。

- 2. (a)當 n-MOSFET 閘極偏壓到達<mark>臨界</mark>電壓(<u>threshold voltage</u>)時,接近界面半導體中的電子電位能會低到接近<u>源</u>極的電子電位能,此時導電電子可開始進入界面,形成通道,稱爲<u>反轉</u>層(<u>inversion layer</u>)。

- (b) 閘極偏壓超過<mark>臨界</mark>電壓後,空乏區寬度就幾乎不再變化,多出的電位差用來增加通到電子,故通道電荷濃度可寫爲 $\frac{Q(x)=Q=-C_{\alpha x}(v_{\alpha s}-V_{\delta})}{t_{\alpha s}}$

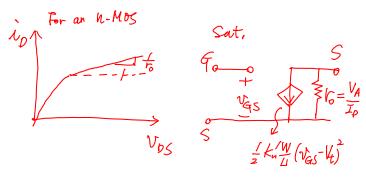

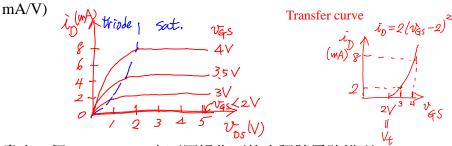

- 3. n-MOSFET 的輸出特性:

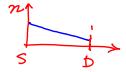

- (a)線性區或 triode 區:

靠近源極必須有導電電子(ON 的條件):  $\nu_{GS} > V_t$  ;

靠近汲極也有導電電子 $\underline{v}_{GD} > V_L$ 或 $\underline{v}_{DS} < \underline{v}_{GS} - V_L$ ;

畫出源極到汲極通道電子的分布示意圖:

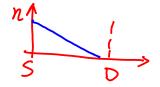

(b)飽和(saturation)區: 注意:和BJT的飽和區完全無關,定義不同。

靠近源極必須有導電電子(ON 的條件):  $\nu_{GS} > V_t$  ;

靠近汲極沒有導電電子:  $\underline{\nu}_{GD} \leq \underline{V}_{\ell}$  或  $\underline{\nu}_{DS} \geq \underline{\nu}_{GS} - \underline{V}_{\ell}$  ;

書出源極到汲極通道電子的分布示意圖:

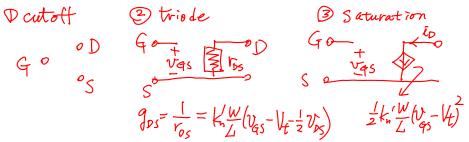

- 4. n-MOSFET 電流電壓特性的計算:

- (a)在很 $v_{DS}$ 小時,通道電荷密度爲 $\underline{-C_{ox}(v_{GS}-V_{t})}$ ,其中單位閘極面積的電容大小爲 $\underline{s_{ox}/t_{ox}}$ 。源極與汲極間電場大小爲 $\underline{v_{DS}/L}$ ,可計算出漂移電流<mark>密度</mark>

大小魚

$$J_n = \mu_n C_{ox} (\upsilon_{GS} - V_t) \frac{\upsilon_{DS}}{L}$$

故汲極電流大小魚

$$i_D = J_n W = \mu_n C_{ox} \frac{W}{L} (\upsilon_{GS} - V_t) \upsilon_{DS} = k_n' \frac{W}{L} (\upsilon_{GS} - V_t) \upsilon_{DS}$$

Process transconductance parameter 定義爲  $\mu_n C_{ox}$  ,單位爲  $A/V^2$  。 (b) 當 $v_{DS}$ 較大時,通道電荷密度不均勻,靠近 $\overline{\mathcal{W}}$ 極處較小,我們取通道中點的值做近似值,如此可得一非線性的 I-V 關係:

$$i_D = \mu_n C_{ox} \frac{W}{L} (\nu_{GS} - V_t - \frac{1}{2} \nu_{DS}) \nu_{DS} = k_n' \frac{W}{L} (\nu_{GS} - V_t - \frac{1}{2} \nu_{DS}) \nu_{DS}$$

當 $v_{DS}$ 愈大時, $i_D$ 對 $v_{DS}$ 的斜率愈小。

- (c)當 $v_{DS}$ 到達 $\underline{v_{GS}}$ 一 $V_L$ 時,靠近汲極的通道<u>夾止</u>(pinch-off),輸出電流就不隨  $v_{DS}$ 變化,形成電流源,此電流源大小與<mark>聞</mark>極偏壓有關。此時的電流可寫爲:  $v_{DS}$   $v_{DS}$  v

- 5. 畫出一個 n-MOSFET 的共源極輸出特性和轉換特性圖:(VT=2V, KP\*W/L=4

6. 畫出一個 n-MOSFET 在不同操作區的大訊號電路模型

- 7. 何謂通道長度調變效應,對 n-MOSFET 的輸出曲線有何影響?請畫出考慮此效應的輸出特性與對應的模型。

- MOSFET 在飽和區時,當 DS 間偏壓愈大,靠近 D 極的空乏區愈大,使得有效的通道長度減小,致使通道電阻減小,導致 ID 上升。